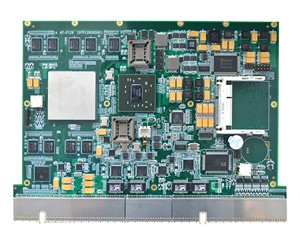

MAR12 Evaluation platform

Platform Introduction

Parameter

1. MPF300T-1152 package in FPGA Microsemi Polarfire series, 300K lookup table, 16 serdes, low-power FPGA.

2. DDR3 2X1GB high-capacity DDR3 memory.

3. Microchip's Cortex-M4 CPU with 1MB of Flash program space.

4. One high-definition HDMI input.

5. HDMI output: One high-definition HDMI output.

6. FPGA external JTAG interface.

7. FPGA onboard Flash Pro debugging tool.

8. An HPC extension interface.

9. A PCIE interface.

10. One 10 Gigabit Ethernet port.

11. One gigabit electrical port, supporting RGMII, GMII, and FPGA communication.

12. One gigabit electrical port, supporting SGMII and FPGA communication (FPGA does not occupy the Serdes interface).

13. LCD screens that support LVDS interfaces.

14. One 1Gb SPI Flash for storage.

15. One 1Gb SPI Flash configuration FPGA.

16. The board DC/DC can be independently controlled by the CPU to control the power on sequence.

17. FPGA can be configured through CPU, onboard FLASH, and onboard Flash pro5.